객체 의 배열 과 초기화

객체의 배열을 정의할떄 각 객체들은 디폴트 생성자로 초기화 된다

객체 의 동적인 생성

기본타입을 동적으로 할당하는 경우에는 커다란 크기의 메모리 공간이 필요한 경우가 대부분이다 단순히int 타입의 변수하나 char타입의 변수하나를 동적으로 생성하는 경우는 극히 드물다 하지만 객체의 경우에는 단순히 객체 하나만을 동적으로 생성하는 경우가 오히려 더많다

객체를 동적으로 생성할때도 new연산자를 사용

생성자와 소멸자의 호출 시점

생성자는 new 연산자를 사용해서 동적으로 객체를 생성할때 호출된다 마찬가지로 소멸자는 delete연산자를 사용해서 해제할때 호출

생성자의 호출 소멸자의 호출

정적인 생성 : 객체를 정의 할떄 정적인 생성 : 객체를 정의한 함수가 끝날때

동적인 생성 : new 연산자로 할당 할때 동적인 생성 : delete 연산자로 해제 할때

정적 멤버 함수에서 객체 생성하기

생성자가 private 로되있다는 점 즉 클래스의 외부에서 객체를 생성하는 것은 블가능하다 하지만 멤버라면 가능하다그래서 정적멤버함수에서 객체를 동적으로 생성해서 그주소를 반환하게 만들었다

- 이렇게 하려면 객체를 동적으로 생성해서 그주소를 반환하는수밖에 없다

ARM 계열의마이크로 프로세서의 역사는 1985년 영국으 Acorn Computers사네서 Berkeley 대학의 RISC프로젝틑 결과를 기반으로 하는 세계 최초의 상업용 RISC 마이크로프로세서인 26비트 어드레스,32비트 데이터에 3단계 파이프 라인 처리 구조를 가지는ARMv1코어를 개발하면서 시작 되었다 이것은 불과 25000개 정도의 트랜지스터를 사용하여 인테의 80286과 비슷하거나 다소 우수한 정도의 성능을 발휘 이어서 1987 년에는 ARMVv1 r 과 유사한 구조를 가지고있지만 32 비트 곱셈기및 캐시 메모리를 내장하고 보조 프로세서를 지원하는 ARMv2가 개발

AT91SAM7S256은 ARM7TDMI제품군에 해당 ARM제품군의 명칭은

ARM{x}{y}{z}{T}{D}{M}{I}{E}{J}{F}-{S}

와 같은 형식으로 표기 각 요소의 의미는

x : 제품군을 표시 7,9,10,11을 사용

y :캐시 MMU를 내장하고있음을 표시 2 = 시와 MMU를 사용 3 = 물리주소 캐시외 MMU를 사용 4 = 캐시와 MPU를 사용 6 = 캐시가없고 쓰기버퍼를 사용 7 = TrustZone 을 사용

z :캐시 메모리를 내장하고있음을 표시 0 = 표준캐시 2 = 감소형 캐시 크기 6 = TCM사용 8 = 가변형TCM사용

T : Thumb instruction set Thumb 모드의16비트 명령어 지원 ARM v6부터는 기본내장

D : Debugger JTAG 인터페이스기능 지원 ARM v5부터는 기본내장

M : Long Multiply instruction 향상된 32 비트X32비트 곱셈명령 지원 ARMv4부터는 기본내장

I : ICE EmbeddedICE 매크로셀을 통하여 하드웨어 브레이크 포인트와 워치포인트 기능지원

E : Enhanced DSP instruction set 향상된 추가 DSP 명령어 지원 AR v6부터는 기본내장

J : Jazelle 명령으로 하드웨어 적인 고속 Java 언어처리 기능지원

F : VFP 부토소수점 연산 보조 프로세서 지우 ㅓㄴ

S : 프로세서 코어를 EDA 툴로 쉽게 사용할수있도록 제공하는 synthesizable버전

∈ AT91SAM7S256의 특징 ∋

① 고성능 16/32 비트 RISC 형의 ARMv4T 구조에 ARM7TDMI 코어를 가지는 ARM Thumb 마이크로프로세서이다.

② ARM의 고성능 32비트 명령 세트와 ARM Thumb의 고밀도 16비트 명령 세트를 가진다.

③ SMA-BA Boot 프로그램을 내장하고 있어서 이는 퍼스널 컴퓨터의 SAM-BA GUI 프로그램과 연계하여 사용자 프로그램을 ISP 방식으로 다운로드한다.

④ 3단계 파이프라인 처리 방식(Fetch/Decode/Execute)을 사용하여 대부분의 명령을 1클록 사이클에 실행하며, 최고 55MHz 이하에서 0.9MIPS/MHz의 명령처리 속도를 나타낸다.

⑤ IEEE Standard 1149.1 규격의 JTAG 인터페이스에 의한 디버그 기능을 가지며, 이밖에도 전용의 UART에 의한 디버그 유닛(DBGU)을 가진다.

⑥ 16개의 32비트 레지스터를 가지는데, 여기에는 스택 포인터와 프로그램 카운터를 포함한다. 이 16개의 레지스터는 5개의 동작모드에서 조금씩 다르게 사용된다.

⑦ 내부에 256KB의 플래시 메모리를 가지고 있는데, 이것은 256바이트x1024 페이지의 구조로 되어 있다. 이것은 10,000번까지 지우고 다시 쓸 수 있으며, 30MHz이하의 속도에서 1사이클에 제로 웨이트로 액세스된다.

⑧ 내부에 64KB의 고속 SRAM을 가지고 있는데, 이것은 55MHz 이하의 속도에서 1사이클에 제로 웨이트로 액세스 된다.

⑨ 메모리 콘트롤러는 버스 조정기, 어드레스 디코더, SRAM 재배치, 플래시 콘트롤러 등의 기능을 가진다.

⑩ 리셋 콘트롤러(RSTC)는 전원투입 리셋 기능과 BOD 기능을 가지며, 리셋 신호를 외부에 출력할 수도 있다.

⑪ 클록 발생기(CKGR)은 32.768kHz의 내부 RC 오실레이터 회로를 가지고 있으며, 또한 외부에 3~20MHz의 수정발진자를 접속할 수 있는 발진 회로도 내장하고 있다. 이들 클록은 PLL 회로에 의하여 적절히 체배될 수 있다.

⑫32비트의 병렬 I/O 포트를 가지고 있는데, 이를 Peripheral A와 Peripheral B등 2개의 주변장치 출력 기능과 멀티플렉스되어 동작하며, 각 핀들은 출력 동자에서 오픈 드레인 또는 10KΩ의 내부 풀업저항을 사용하도록 설정할 수 있다.

⑬ AT91SAM7S256은 모두 산업용 버전으로서 -40˚C ~ +85˚C의 온도 범위에서 사용할 수 있다.

⑭ ARM사는 반도체 제조회사가 아니며 ARM마이크로 프로세서 제품을 직접 만들지 않는다

⑮ 가격이싸다

ARM 마이크로 프로세서의 내부에는 고성능의 AMBA버스구조 를 사용한다 AMBA버스에는 내부 시스템버스로 사용되는 고성능의 AHB 및ASB버스와 이보다는 느리지만 내부의 주변장치를 접속하는데 유용한 APB 버스등 3가지가 있다

AT91SAM7S256 의 내부구조

전체구조

AT91SAM7S256의 내부 구조를보면 이것은 ARM7TDMI 형의 CPU코어에 기본적으로 JTAG 인터페이스가 부속되며 내부의 시스템버스 ASB를 통하여 메모리 제어기와 플래시 메모리 및 SRAM 이 연결되어 있다 또한 플래시 메모리의 옆에는 별도로 SAM-BA Boot프로그램이 저장되어 있는 ROM 이있다

CPU 구조

AT91SAM7S256 의 CPU 코어는 ARM7TDMI 에 해당 ARM7TDMI 구조의 CPU 코어는 고성능의 32비트 ARM 명령과 고밀도의 16비트 Thumb명령을 모두 실행 할수있는 데 이것은 ARMv4T의 폰노이만 방식을 기반으로 하는 RISC형 마이크로 프로세서로서 3단계의 파이프라인 처리방식Instruction Fetch(F) - Instruction Decode(D) - Execute(E)로 명령을 처리한다

ARM7TDMI CPU코어는 명령을 인출하여 해독하고 실행하는 로직회로와 레지스터 뱅크 ,32비트 ALU,32x8비트의 하드웨어 곱셈기,배럴시프터 등으로 구성되며 여기에 별도로 JTAG 인터페이스 회로가 추가된다

ARM7TDMI CPU는 8비트의 바이트데이터 ,16비트 하프워드데이터,32 비트의 워드데이더를 처리할수있다

- 하프워드 데이터 = 2바이트 경계로 할당 ,저장

- 워드 데이터 = 4바이트 경계로 할당, 저장

ARM7TDMI 코어에는 CPU가 7가지의 동작모드를 가지고있다 User Mode 를 제외한 모든 동작모드를 특권모드 라고 하는데 여기서는 시스템 자원을 모두 엑서스 ,동작 모드를 자유롭게 변경 UserMode 와 SystemMode를 제외한 5개의 동작모드를 예외 모드 이들모드에는 특별한예외가 발생하였을떄 만 진입

- UserMode : 일반적인 ARM프로그램을 실행하는 상태

- System Mode : 운영체제를 위한 사용자 특권 모드

- FIQ Mode : 고속의 데이터 전송이나 채널처리를 지원하는 인터럽트 처리모드

- IRQ Mode : 범용의 인터럽트 처리모드

- Supervisor Mode : 운영체제를 위한 프로텍티드 모드

- Abort Mode : 가상 기억장치나 메모리 보호를 구현하는 모드

- Undefined Mode : 하드웨어 보조 프로세서를 소프트웨어적으로 에뮬레이션 하는 모드

ARM Register의 종류

l 31개의 범용 레지스터

1. 대부분의 연산에 사용됨

2. 동작모드에 따라 사용이 제한

l 1개의 CPSR

1. Current Processor Status

2. 프로세서가 수행하고 있는 현재의 동작 상태를 나타냄

l 5개의 SPSR

1. Saved Processor Status

2. 이전 모드의 CPSR 복사본

3. Exception이 발생하면 ARM이 하드웨어적으로 이전 모드의 CPSR값을 각각의 모드에 해당하는 SPSR에 복사

4. System Mode를 제외한 모든 Privilege Mode에 각각 하나씩 존재

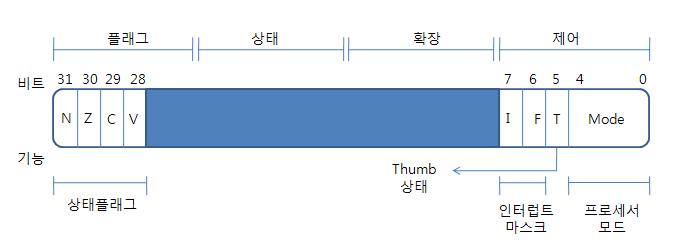

CPSR레지스터

- ARM 코어는 내부 동작을 모니터링하고 제어하기 위해 사용함.

- 전용 32 비트 레지스터, 레지스터 파일에 위치함.

[ 일반적인 프로그램 상태 레지스터(psr) ]

- 8비트씩, 플래그(Flag), 상태(Status), 확장(Extension), 제어(Control)의 네 영역으로 나뉜다.

- 상태, 확장 필드는 미래에 사용할 목적으로 예약( 색칠된 부분 )

- 제어 필드에는 프로세서 모드와 상태, 인터럽트 마스크 비트가 포함되어 있다.

- 플래그 필드에는 상태 플래그가 저장되어 있다.

추가로 할당된 비트들.

- J 비트 : Jazelle(8비트 자바 명령어)이 가능한 프로세서에서만 사용 가능함.

- 추후 모니터링이나 새로운 기능 제어를 위해 추가로 비트 할당할거임

예외처리 벡터에 사용되는 명령

ARM의 예외처리 벡터의 주소에는 하나의 ARM 명령이 사용된다.

따라서 벡터 테이블에 분기 명령 또는 이와 유사한 분기 가능한 명령을 사용하여

실제 예외처리를 위한 핸들러로 분기하도록 되어있다.

분기 명령

B 명령은 예외처리 백터에서 사용되는 가장 일반적인 명령이다.

분기할 수 있는 주소 영역은 PC 값을 기준으로 +-32MB 내에 있어야만 사용이 가능하다.

MOV 명령

MOV 명령을 사용하고, PC를 대상 레지스터로 하면 분기 명령과 동일하게 동작된다.

ex) MOV PC, #0x80000000

오퍼랜드 2의 특성에 따라 8비트로 표현할 수 있고,

만약 핸들러가 0x800000010와 같이 8비트로 표현되지 않으면 MOV 명령은 사용할 수 없다.

LDR 명령

B 또는 MOV 명령으로 분기할 수 없는 위치에 핸들러가 있는 경우에는 비록 메모리 액세스 사이클이 필요하지만 데이터 전송 명령인 LDR 명령을 사용할 수 있다. 이 방법은 PC-Relative 주소지정 방식을 이용하여 리터럴 풀에 어드레스를 저장하고, 32비트 어드레스를 PC에 읽어 오는 방법이다.

ex) LDR PC, =0x80030000

예외처리와 명령어 파이프라인

ARM이 외부에서 발생되는 예외처리를 인식하고 처리하는 시점은

명령어 파이프라인과 밀접한 관계가 있다.

| 예외처리 |

명령 파이프라인 |

PC 복원 |

| Undefined Instruction |

Decode |

PC := LR |

| SWI (Software Interrupt) |

Decode | PC := LR |

| Prefetch Abort |

Execute | PC := LR - 4 |

| Data Abort |

Memory | PC := LR - 8 |

| IRQ | Execute | PC := LR - 4 |

| FIQ | Execute | PC := LR - 4 |

예외처리 복귀

예외처리가 완료되면 다음과 같은 프로그램으로 이전 상태로 되돌아 갈 수 있다.

PC 값을 LC_<mode>로부터 복원한다.

SPSR_<mode>를 CPSR에 복원한다.

이 때 두가지 일이 동시에 이루어져야 한다. 예외처리에서 복귀하는 동작을 하나의 명령으로 처리하기 위하여 다음과 같은 2가지 명령을 사용할 수 있다.

데이터 처리 명령과 'S' 접미사 사용

데이터 처리 명령에 S 접미사를 사용하고, PC를 대상 레지스터로 지정하면

CPSR 값이 복원되면서 PC도 LR을 이용하고 계산하고 복원하는데 용이하다.

ex) SUBS PC, LR, #4

MOVS PC, LR

LDM 명령과 '^' 사용

예외처리가 끝날 때 스택에 저장되어 있는 범용 레지스터도 같이 복원된다. 스택에서 POP하는 경우 ARM은 보통 LDM 명령을 많이 사용한다. ARM에서는 LDM명령을 사용하여 범용 레지스터 복원과 CPSR 값 복원을 동시에 하는 방법을 제공한다.

ex) LDM SP!, {R0, R1, R2, PC}^

메모리구조

AT91SAM7S256 의 메모리 구조는 3개의 1MB짜리 메모리 영역과 256MB짜리 내장 주변장치 영역으로 나누어진다

플래시 메모리영역은 0x0010_0000~0x001F_FFFF의 1MB영역이지만 실제로는 0x0010_0000~0x0013_FFFF번지에 256KB으 ㅣ 플래시 메모리를 가지고있으며 SRAM 영역은0x0020_0000~0x002F_FFFF의 1MB영역이지만 실제로는 0x0020_0000~0x0020_FFFF 번지에 64KB의SRAM을 가지고있다

메모리 맵핑

AT91SAM7S256의 0x0000_0000~0x000F_FFFF 의 1MB 영역은 실제로 메모리가 존재 하지않지만 플래시 메모리또는 SRAM 이 이곳으로 맵핑되어 메모리가 존재하는 것처럼 동작하는 영역

플래시 메모리 보호기능

내장 플래시 메모리 콘트로럴(EFC)는 플래시 메모리에 관한 기능을 제어하는 데 이것은 웨이트 사이클을 설정하거나 플래시 메모리의 삭제 프로그래밍 액세스 등에 관련된기능을 수행한다 이런한 플래시 메모리관련동작에는 보호기능이 포함 되는데 EFC는 이를 위하여 16개의 록비트,1개의 안전비트 2개의 GPNVM비트등과 같으 NVM비트들을 가지고있다

- 록비트

16개의 록비트는 플래시 메모리 록영역을 하나씩 개별적으로 제어하는 기능을 수핼 AT91SAM7S256에서 1개의 록영역은 256 바이트짜리 페이지가 64개로구성되므로 16KB의 크기를 가진다

- 안전비트

1개의 안전비트는 JTAG ICE나 FFP인터페이스 등 어떤 방법으로도 플래시 메모리를 액세스하는것을 금지함으로써 플래시 메모리에 들어있는 코드의 비밀을 유지하는데 사용

- GPNVM비트

2개의 GPNVM 과 GPNVM1 비트는 저전압 검출기(BOD)의 동작을 제어하기 위하여 사용

플래시 메모리 프로그래밍 기능

AT91SAM7S256 의 플래시 메모리릴 사용자가 프로그랭밍하는데 3가지 방법이 있다

1) JTAG인터페이스를 사용하는 방법 이는 대부분 에뮬레이터라는 특별한 장비를 필요

2) 플래시 프로그래밍 인터페이스(FFPI)를 이용하는 방법 이를 사용하려면 리셋직후에 TST핀은 1로 입력하고 동시에 PA0=PA1,PA2=0으로해야한다

3) SAM-BA Boot 프로그램과 USB 또는DBGU 포트를 이용하는 방법으로 이를 사용하려면 리셋직후에 TST핀을 1로 입력하고 동시에PA0=PA1

=PA2=1로 해야한다

ARM명령의 개요

ARM명령은 기본적으로 다음과 같은 형식으로 구성

ADD{cond}{S} Rd,Rn,Op2 {; Rd <-- Rn + Op2}

여기서 cond 는 이 명령이 실행되는 조건을 나타내는 접미사이다 거의 대부분 ARM명령은 이와같이 조건부실행 이조건은 명령의 기계어 코드에서 항상 최상위의 4비트인 b31~b28 에 인코딩되어 표시

S 는 이명령을 실행한후에 CPSR 레지스터의 조건 플랙을 업데이트 하라는 의미 이를 생략하면 조건 플랙은 변화되지않고 현재의 값을 유지 Rd 는 처리 결과가 저장되는 목적 오퍼랜드 이고 Rn은 제1소스오퍼랜드 이며 Op2는 제2소스 오퍼랜드 이다 ADD명령 에서는 이처럼 3개의 오퍼랜드를 사용 명령에 따라서는 이들 오퍼랜드 의 일부또는 전부가 없는 경우도 있다

조건부 실행

모든 ARM 명령어에는 조건부 실행이 가능하도록 최상위 비트 [31:28]에 조건 필드를 가지고 있으며, 명령이 실행될 때 이 비트와 CPSR의 조건 플래그의 조건을 검사하여 명령의 실행 여부를 결정하는데 사용된다.

조건에 따라 명령어를 실행하도록 하기 위해서는 적절한 조건을 접미사로 붙여주면 되는데,

조건이 명시되지 않으면 'Always'로 동작한다.

|

명령의 접미사 |

CPSR의 플래그 |

의미 | |

|

0000 |

EQ |

Z set |

같다. |

|

0001 |

NE |

Z Clear |

같지 않다. |

|

0010 |

CS |

C set |

크거나 같다. (unsigned) |

|

0011 |

CC |

C clear |

작다. (unsigned) |

|

0100 |

MI |

N set |

음수 (Negative) |

|

0101 |

PL |

N clear |

양수 (Positive) 또는 0 |

|

0110 |

VS |

V set |

오버플로우 |

|

0111 |

VC |

V clear |

오버플로우가 발생하지 않음 |

|

1000 |

HI |

C set && Z clear |

크다. (unsigned) |

|

1001 |

LS |

C clear |

작다. (unsigned) |

|

1010 |

GE |

N == V |

크거나 같다. |

|

1011 |

LT |

N != V |

작다. |

|

1100 |

GT |

Z clear && ( N == V) |

크다. |

|

1101 |

LE |

Z set || (N !=V) |

작거나 같다. |

|

1110 |

AL |

Always |

무조건 실행 |

ex>

무조건 실행 -> ADD r0,r1,r2

조건부실행 -> ADDEQ r0,r1,r2

조건 플래그의 설정은 명령어에 'S' 접미사를 삽입한다.

데이터 처리 명령의 경우 'S'접미사가 없으면 조건 플래그에 영향을 미치지 않는다.

ex> SUBS r0,r1,r2

하지만 데이터 처리 명령 중 비교를 위한 명령은

별도로 'S'접미사를 삽입하지 않아도 조건 플래그가 설정된다.

분기 명령어

ARM의 분기 명령은 Branch(B)와 Branch with Ling(BL) 명령이 있다.

BL명령은 함수를 호출할 때 많이 사용되는데 되돌아올 주소를 링크 레지스터(LR)에 저장한다.

31 28 27 25 24 23 0

|

Cond |

101 |

L |

Offset |

B{L}{cond} <expression>

{L}은 branch with link로 R14(LR)에 PC 값을 저장하도록 한다.

{cond}는 조건부 실행을 위한 조건을 나타낸다.

<expression>은 분기하고자 하는 위치 정보를 나타낸다.

Branch with Link와 함수 호출

BL 명령이 사용되면 되돌아올 주소가 LR(R14)에 저장된다.

BL 명령이 실행될 때의 PC 값을 LR에 저장한 후 조절 과정을 통하여 BL 명령 다음의 주소를 LR에 저장하는 방식으로 이루어진다. 따라서 호출된 함수에서 되돌아 갈 때에는 LR 값을 PC에 복원하면 BL 다음 명령부터 새롭게 명령이 패치되면서 프로그램이 실행된다.

함수 리턴 MOV PC, LR

Branch와 Branch with Link 명령의 옵셋

B 또는 BL 명령에서 <expression>은 분기하고자 하는 레벨을 표시한다.

이 레벨은 2진 명령 구조로 표현될 때 PC 값을 기준으로 하여 명령 구조의 비트 [23:0]의 옵셋 필드에 기록된다. 앞 또는 뒤로 분기를 하기 위한 +- 정보를 위해 1비트를 사용하고, PC에서 분기 위치까지의 정보가 23비트에 기록되는데, 이 때 2비트 쉬프트되어 기록된다. 따라서 분기 가능한 위치는 현재 명령이 사용되는 위치를 기준으로 +-32MB를 넘지 못하도록 되어 있다.

데이터 처리 명령어

레지스터에 저장되어 있는 값을 이용하여 연산을 수행하고

그 결과를 다시 레지스터에 저장하는 명령을 말한다.

데이터 처리 명령은 산술연산, 논리연산, 데이터 MOVE 명령, 비교 명령으로 이루어져 있다.

Rd는 연산 결과가 저장되는 레지스터, Rn은 연산에 사용되는 첫 번째 오퍼랜드, Op2는 연산에 사용되는 두 번째 오퍼랜드다.

31 28 27 26 25 24 21 20 19 16 15 12 11 0

| Cond |

00 |

I |

OpCode |

S |

Rn |

Rd |

Operand 2 |

산술연산 명령

| 0100 | ADD |

더하기 |

Rd := Rn + Op2 |

| 0101 | ADC | 캐리와 함께 더하기 |

Rd := Rn + Op2 + Carry |

| 0011 | SUB | 빼기 | Rd := Rn - Op2 |

| 0110 | SBC | 캐리와 함께 빼기 |

Rd := Rn - Op2 - 1 + Carry |

| 0011 | RSB | 역으로 빼기 |

Rd := Op2 - Rn |

| 0111 | SRC | 캐리와 함께 역으로 빼기 |

Rd := Op2 - Rn - 1 + Carry |

논리연산 명령

| 0000 | AND |

AND |

Rd := Rn AND Op2 |

| 1111 | ORR | OR | Rd := Rn OR Op2 |

| 0001 | EOR | Exclusive OR |

Rd := Rn XOR Op2 |

| 1110 | BIC | Bit clear |

Rd := Rn AND (NOT Op2) |

비교연산 명령

| 1010 | CMN |

Negative를 취해 검사 |

CPSR flags := Rn + Op2 |

| 1011 | CMP | 비교 | CPSR flags :=Rn - Op2 |

| 1000 | TEQ | 비트 단위로 EOR 검사 |

CPSR flags :=Rn EOR Op2 |

| 1001 | TST | 비트 단위 검사 |

CPSR flags := Rn AND Op2 |

데이터 MOVE 명령

| 1101 | MOV |

레지스터나 상수 이동 |

Rd := Op2 |

| 1111 | MVN | Negative를 취해 이동 |

Rd := 0xFFFFFFFF EOR Op2 |

데이터 처리 명령과 내부 버스

소스 레지스터인 Rn은 레지스터 뱅크에서 A 버스를 통하여 ALU에 전달되고,

오퍼랜드 2는 B 버스와 배럴 쉬프터를 통하여 ALU에 전달된다. (따라서 Op2는 쉬프트 동작가능)

연산 결과는 ALU 버스를 통하여 레지스터 뱅크의 대상 레지스터에 저장 된다.

오퍼랜드 2와 배럴 쉬프터

오퍼랜드 2는 레지스터 또는 이미디어트 상수의 형태를 가질 수 있다.

사용 여부는 명령어의 비트[25]에 의하여 결정된다.

오퍼랜드 2로 레지스터가 사용되는 경우

| 비트 [6:5] |

쉬프트 동작 |

| 00 | Logical Shift Left |

| 01 | Logical Shift Right |

| 10 | Arithmetic Shift Right |

| 11 | Rotate Right |

오퍼랜드 2로 이미디어트 상수가 사용되는 경우

ARM 명령은 32비트로 구성되어 있고, 오퍼랜드 2는 명령어의 비트[11:0], 12비트로 구성되어 있다.

따라서 다음과 같이 12비트로 32비트를 표현한다.

11 8 7 0

| #rot | 8비트 #imm |

비트[7:0]의 8비트 상수가 비트[11:8]의 4비트 로테이트 값에 2를 곱한만큼 로테이트 라이트(RR)하여

나온 값을 사용한다. 따라서 항상 이미디어트 상수로 사용되는 값은 8비트로 표현해야 한다.

즉 0xFF000000, 0x00F70000, 0x00000009와 같이 비트 1의 시작에서부터 끝까지가 8비트로 사용할 수 있어야한다. 0x000001FF, 0x10300000과 같이 8비트 내에 표현할 수 없으면 사용할 수 없다.

PSR 전송 명령어

PSR 전송 명령은 CPSR, SPSR 두 종류의 레지스터와 ARM의 범용 레지스터 R0~R15 사이에 데이터를 전송하는 명령이다. 하지만 CPSR의 T 비트에는 임의의 값을 기록할 수 없다.

| PSR | User 모드 |

그 밖의 특권 모드 |

| CPSR | 액세스 불가 |

해당되는 SPSR만 액세스 |

| SPSR | 조건 플래그 부분에만 기록 |

모든 필드에 기록이 가능 |

MRS - PSR 레지스터의 값을 ARM의 범용 레지스터로 읽어오는 명령

MSR - 범용 레지스터, 이미디어트 상수 값을 PSR 레지스터로 전송하는 명령

곱셈연산 명령어

ARM의 곱셈 명령은 레지스터에 저장된 두 개의 32비트 레지스터를 곱하는 연산을 수행한다.

32비트 곱셈 명령에서는 하위 32비트만 대상 레지스터에 저장하고,

64비트 곱셈 명령에서는 2개의 대상 레지스터에 32비트씩 결과를 나누어 저장한다.

| 000 |

MUL |

32bit Multiply |

Rd := (Rm * Rs) [31:0] |

| 001 | MLA | 32bit Multiply-accumulate |

Rd := (Rm*Rs+Rn) [31:0] |

| 100 | UMULL | 64bit Unsigned Multiply |

RdHi:RdLo := Rm*Rs |

| 101 | UMLAL | 64bit Unsigned Multiply-accumulate |

RdHi:RdLo += Rm*Rs |

| 110 | SMULL | 64bit Signed Multiply |

RdHi:RdLo := Rm*Rs |

| 111 | SMLAL | 64bit Signed Multiply-accumulate |

'코스웨어 > 10년 스마트폰BSP' 카테고리의 다른 글

| [BSP]업무일지-김 진-20100629 (1) | 2010.06.30 |

|---|---|

| [BSP]-업무일지-정홍환-20100628 (1) | 2010.06.28 |

| [BSP]업무일지-강혜정-20100625 (0) | 2010.06.26 |

| [BSP]업무일지_차상목_20100624 (0) | 2010.06.24 |

| [BSP]업무일지-박동수-20100622 (0) | 2010.06.22 |

| [BSP]업무일지-한정효-20100621 (0) | 2010.06.21 |

| [BSP]업무일지-송동규-20100618 (0) | 2010.06.19 |

| [BSP]업무일지-김동훈-20100617 (0) | 2010.06.18 |