20150324 S/W

스마트 컨트롤러 - 시리얼 통신 UBRR register

· Atmega 데이터 시트를 보고 Clock을 조정 할 수 있는 레지스터인 UBRR은 Baud Rate Generator을 조작하여

속도를 조절 할 수 있다.

· UDR은 전송할 정보를 입력하면 Transmit Shift Register에 해당 정보를 전달한다. Shift Register라고 칭하는 이유 는 병렬식이 아닌 직렬식이기 때문에 데이터를 하나를 밀어서 전송하기 때문이다.

· Shift Register 시리얼 통신을 하는 기기에서 보내는 쪽 받는 쪽 모두 필요 하다.

· Shift Register라고 칭하는 이유는 병렬식이 아닌 직렬식이기 때문에 데이터를 하나를 밀어서 전송하기 때문이다

· Baud Rate Generator는 보기 1번과 2번 구분 하는 역할을 하기도 한다. 보기 1번과 2번처럼 1이나 0의 길이를

판단하는 역할도 한다.(데이터 판단)

· UDR의 주소는 같지만 해당주소 안에서 Transmit영역과 Receive영역으로 나뉜다. 송신과 수신에 따라 UDR은

명령어를 자동 분류하여 명령어를 해석한다.

· ARM CPU는 UDR의 송수신 레지스터가 따로 분리되어 있다.

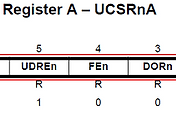

SMART.H 파일에 UCSRA, UCSRB, UCSRC 추가 시킴

· SMART.H에 UCSR을 아트메가 데이터 시트를 참조하여 define 한다.

fosc = Frequency of oscillator = 16,000,000

BAUD = 115.200(통신속도)

BIT = 16

*UBRR = fOSC/16*BAUD - 1

표 20-1을 참고해서 위의 계산식을 적용해서 값을 넣거나 표(20-12)를 보거 넣거나 하는 방식으로

값을 넣어준다.

UBRR register 표를 보면

앞에 4bit를 사용하지 않고 뒤에 12bit만 쓴다.

이진수 bit를 flag로 비유하기도 한다.

set = 1, clear = 0

7번 bit는 버퍼가 차 있는지 아닌지를 표시해준다.(전송시 1, 비전송시 0)

디지털 제어 - 가산기 실습 대비 및 회로도 연습

학습목표

반가산기와 전가산기를 OrCAD로 그릴 수 있다.

반가산기와 전가산기를 브레드보드에 만들 수 있다.

1. 프로테우스에 회로도를 그려본 후 제대로 작동하는지 확인해보자.

2. 작동을 확인한 후에 OrCAD로 회로도를 그려보자.

3. 브레드 보드에 회로를 만들어 보자.

<74HC86>

<74LS00>

<74LS14>

<74HC32>

'코스웨어 > 15년 스마트컨트롤러' 카테고리의 다른 글

| 20150326-7번 김성현 pic를 이용한 count up &down ,UART (6) | 2015.03.27 |

|---|---|

| 20150326 USART_소스입니다. (1) | 2015.03.26 |

| 20150325-6번-김성주-S/W-UCSRnA,B,C #define 설정 및 초기화 (13) | 2015.03.25 |

| 20150325-6번-김성주-H/W-PIC16F917을 이용한 LED 점등 (5) | 2015.03.25 |

| 20150323-3번-권오민 - 시험대비 정리(개인) / Serial Cable & USART (16) | 2015.03.23 |

| 20150320 주보건 소스파일 (0) | 2015.03.23 |

| 20150320-2번-강동조-발진회로&LCD문자표현 (10) | 2015.03.20 |

| 20150320 강동조 소스파일입니다 (0) | 2015.03.20 |